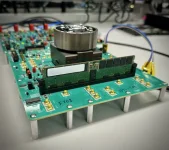

Cadence created the first DDR5 12.8 Gbps MRDIMM Gen 2 memory IP system for TSMC N3 process. This solution helps meet growing memory needs for AI processing in data centers. The new Cadence DDR5 IP comes with a complete memory subsystem that doubles bandwidth compared to current DDR5 6400 Mbps DRAM parts. It offers flexible design options with architecture that lets users adjust power and performance for specific applications.

Micron supports this technology with their advanced DRAM to handle AI workloads better. Montage Technology provides memory buffers that work with Cadence's solution to deliver high performance for servers. These partnerships show how important this technology is for next-generation data centers. Boyd Phelps from Cadence mentions that many large customers want this innovative technology for their future products.

The system uses Cadence's Verification IP for testing, making it easier to check everything works correctly from the IP to the full system level. This verification includes DFI VIP, DDR5 memory model, and System Performance Analyzer tools. The complete package helps companies build faster AI systems with reliable memory performance.

Micron supports this technology with their advanced DRAM to handle AI workloads better. Montage Technology provides memory buffers that work with Cadence's solution to deliver high performance for servers. These partnerships show how important this technology is for next-generation data centers. Boyd Phelps from Cadence mentions that many large customers want this innovative technology for their future products.

The system uses Cadence's Verification IP for testing, making it easier to check everything works correctly from the IP to the full system level. This verification includes DFI VIP, DDR5 memory model, and System Performance Analyzer tools. The complete package helps companies build faster AI systems with reliable memory performance.